# Chapter 6 DEVELOPMENT AND DESIGN OF THE CONTROL CIRCUIT FOR QUASI-RESONANT CONVERTER

# **6.1 Introduction**

This chapter describes the basic principles of operation and control of quasi-resonant converter for induction melting application. In induction melting application the load is variable which depends on the type & quantity of metal to be melted. Thus the output frequency should be automatically adjusted to suit changing load condition, so that the converter always operates at the resonance frequency of tank circuit.

# 6.2 Control

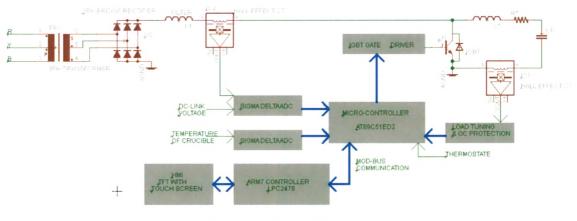

Control of the output frequency and output power of the converter is effected by command triggers to the converter. The control scheme is shown in Figure 6-1.

Figure 6-1 Control Scheme

Three distinct control loops are utilized in controlling the output of the converter.

They are:

- 1. Self control of the ON duty cycle by timing the converter switching from the induction load,

- 2. Control of output frequency and power by closed loop control through D-C Link power feedback.

- 3. Current limit for mishaps of short circuits by closed loop control.

Figure 6-2 Variable Load

Self-controlling the output frequency allows the converter to adjust itself to compensate for variations encountered with induction loads as shown in Figure 6-2. When the driving frequency is the resonant frequency of the tank circuit, the capacitive and inductive currents cancel each other, the input power factor is unity, and the generator supplies only real current and real power to the load. If the magnetic work piece is heated through the Curie temperature, or if it is removed from the crucible, the magnetic permeability of the flux path inside the coil is reduced to unity, and the generator is decreased. The inductor current increases, the capacitor current no longer equaling it, and the generator is forced to supply a large lagging current. Thus compensation is required to be automatically made by control which should sense the increase in the tank natural resonant frequency and should speed up the switching rate of the converter.

As shown in Figure 6-1, the hall effect CT is used to sense the high frequency current in the tank circuit. The details about it are in the following topic.

## 6.3 Current Sensing Technology Overview

There are three technologies that are typically used for measuring current: sense resistors, current transformers and Hall effect sensors.

Sense resistors are simply a resistor placed in series with the load. By ohms law, the voltage drop across the device is proportional to the current. For low currents, these provide very accurate measurement given the resistance value has a tight tolerance.

Although sense resistors with high performance thermal packages have been developed for larger currents, they still result in insertion loss. In addition, they do not provide a measurement isolated from transient voltage potentials on the load. Sense resistors also require other circuitry such as instrumentation amplifiers to generate a distinguishable signal.

Current transformers are relatively simple to implement and are passive devices that do not require driving circuitry to operate. The primary current (AC) will generate a magnetic field that is coupled into a secondary coil by Faraday's Law. The magnitude of the secondary current is proportional to the number of turns in the coil, which is typically as high as >1000. The secondary current is then sensed through a sense resistor to convert the output into a voltage.

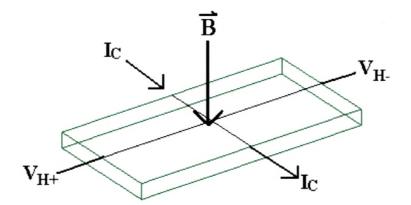

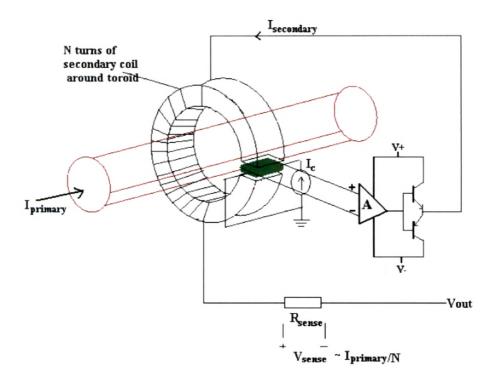

There are two techniques for sensing current using Hall effect devices. According to the Hall effect, a magnetic field passing through a semiconductor resistor will generate a differential voltage proportional to the field (figure 6-3).

Figure 6-3 Representation of the Hall effect and its electrical parameters

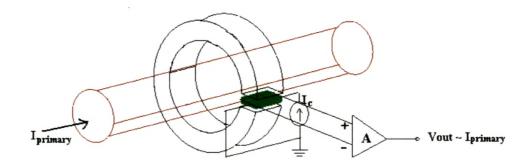

Concentric magnetic field lines are generated around a current carrying conductor. Approximating the primary current conductor as infinitely long, the magnetic field strength may be defined  $B = \mu oI/2pr$ , where  $\mu o$  is the permeability of free space, I is the current and r is the distance from the center of the current conductor. In order to induce a larger signal out of the Hall element; the current conductor may be wrapped around a slotted ferrous toroid N number of times, such that  $B = \mu oNI/2pr$ . In an open loop topology, the Hall element output is simply amplified and the output is read as a voltage that represents the measured current through a scaling factor as depicted in figure 6-4.

Figure 6-4 Basic Topology of Open Loop Hall Effect Current Sensor

In a closed loop topology, the output of the Hall element drives a secondary coil that will generate a magnetic field to cancel the primary current field. The secondary current, scaled proportional to the primary current by the secondary coil ratio, can then be measured as voltage across a sense resistor.

Figure 6-5 Basic Topology of Close Loop Hall Effect Current Sensor

By keeping the resultant field at zero, the errors associated with offset drift, sensitivity drift and saturation of the magnetic core will also be effectively canceled. Closed-loop Hall effect current sensors also provide the fastest response times. However, with a secondary coil that may be needed to drive up to several milli-amps of current, power consumption is much higher in closed loop Hall effect devices than open loop topologies. The closed loop configuration also limits the magnitude of the current that can be sensed since the device may only drive a finite amount of compensation current.

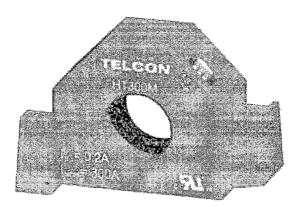

Thus for this application HT300M (Figure 6-6) is used to measure the tank current as its bandwidth is DC to 115kHz at -3dB and the frequency of operation is 7-8khz.

### DEVELOPMENT AND DESIGN OF ...... QUASI-RESONANT CONVERTER

Figure 6-6 Hall Effect Current Sensor Panel Mounting Type HT300M

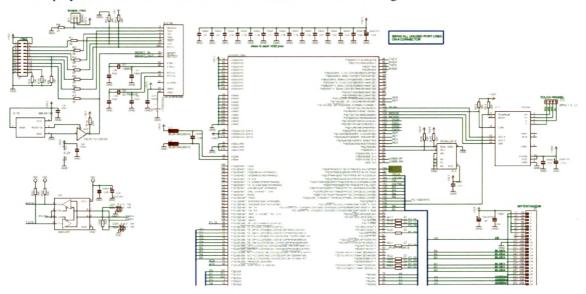

The whole scheme of Figure 6-1 is divided into two boards:

- 1. Micro-controller Board (AT89C51ED2).

- 2. Embedded controller (Arm-7) Board.

These two cards interact with each other through MOD-BUS communication protocol.

# 6.4 Micro-controller Board (AT89C51ED2)

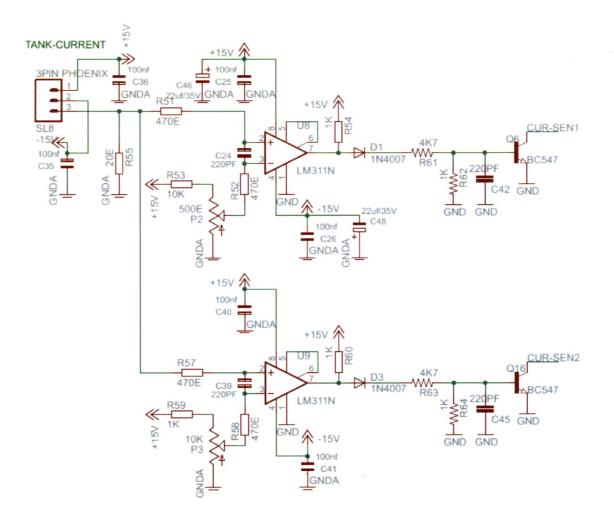

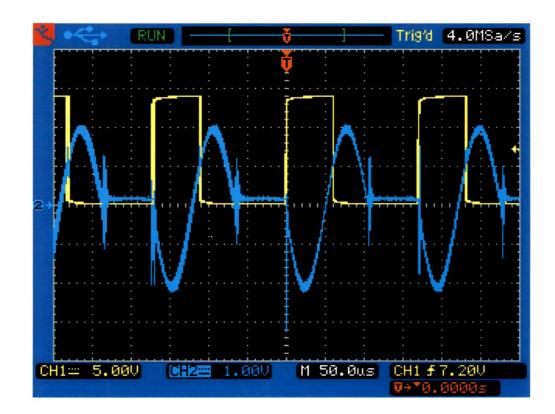

The self controlling is accomplished by micro-controller card, which takes the tank current as input (through hall-effect current sensor) & with load tuning circuit as shown in Figure 6-7 controls the on cycle duty of IGBT firing pulses. The Tank current is compared with the preset voltage (0.1V) to generate a falling edge as shown in Figure 6-8 on CUR-SEN1 pin which is connected to INTO\_. This automatically compensates for the changes in load inductance. The second comparator compares for the over current and informs micro-controller about it.

Figure 6-7 Load Tuning and Over Current Protection Circuit

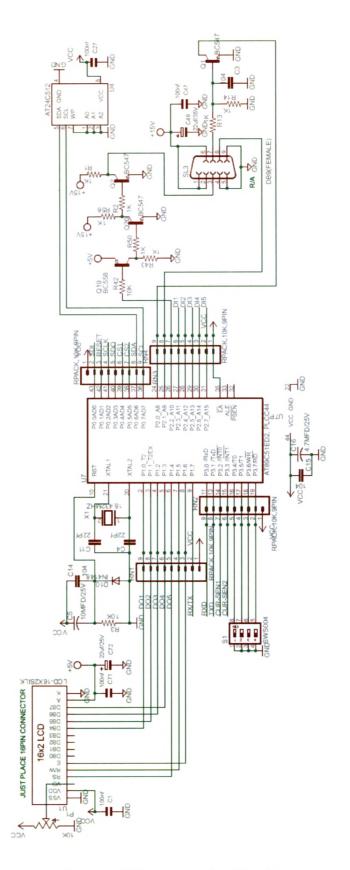

Figure 6-9 Micro-controller Circuit

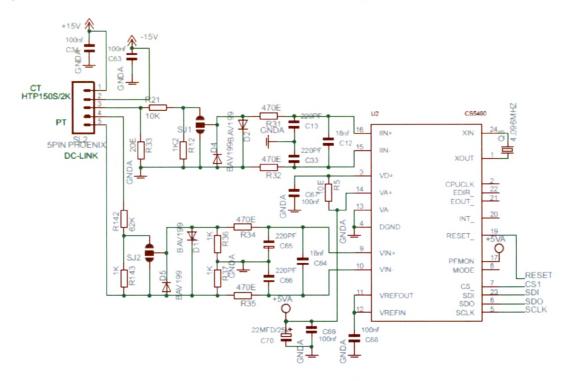

Besides above function the microcontroller card digitizes the DC-Link Voltage & Current using a Sigma-Delta ADC and calculates DC-Link Power as shown in Figure 6-10.

Figure 6-10 Measurement of DC-Link Voltage & Current

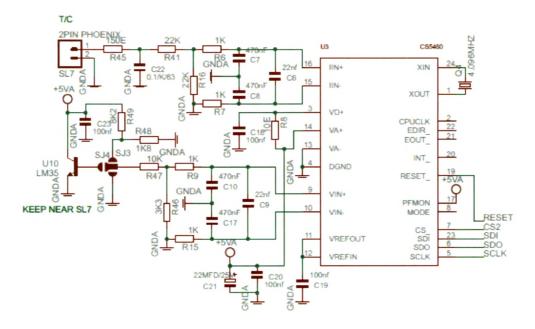

Using second Sigma-Delta ADC it measures the temperate of crucible through thermocouple & does cold junction compensation as shown in Figure 6-11.

Figure 6-11 Measurement of Crucible Temperature

Finally these two quantities are sent to the ARM-7 card through RS-485 for further processing. After processing on these data the ARM-7 card decides about operating frequency and the frequency bursts which are then sent out to micro-controller card through RS-485. The micro-controller card taking these commands finally controls the converter.

## 6.5 Embedded controller (ARM-7) Board (LPC2478)

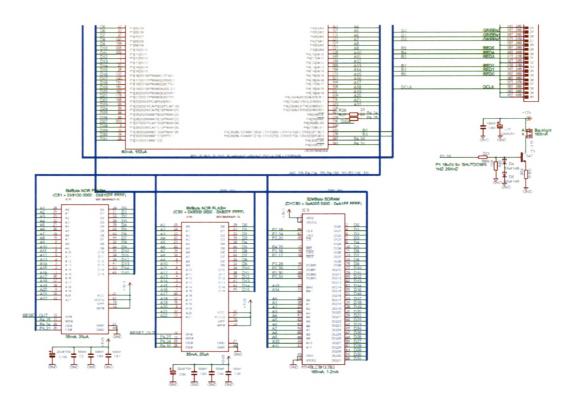

Figure 6-12 depicts the Arm-7 controller board. The core part of the design is the NXP LPC2478 microcontroller. NXP Semiconductors designed the LPC2478 microcontroller, powered by the ARM7TDMI-S core, to be a highly integrated microcontroller for a wide range of applications that require high-speed calculations, advanced communications and high quality graphic displays. The LPC2478 microcontroller has 512 kB of on-chip high-speed flash memory. This flash memory includes a special 128-bit wide memory interface and accelerator architecture that enables the CPU to execute sequential instructions from flash memory at the maximum 72 MHz system clock rate. The on-chip UART peripheral includes a fractional baud rate generator that allows standard baud rates to be generated with low frequency error. There is a 32.768 kHz crystal clock for the on-chip real-time clock peripheral unit or RTC for short. Power for the RTC (during these low power modes) comes from the VBAT input pin.

As the major function of ARM-7 board is to do processing on data received from Micro-controller card and to interface TFT with touch screen the LPC2478 becomes to ultimate choice with respect to price & performance. As seen in Figure 12-6a TSC2046 is used to interface touch screen while the bottom part shows the interfacing of TFT display (800x640). In Figure 12-6a the interfacing of SDRAM (MT48LC8M32B2) and NOR FLASH (SST39VF6401-70) is shown. The SDRAM is used as the display RAM while NOR-FLASH is used to store constant images.

Figure 6-12a ARM-7 control board

## DEVELOPMENT AND DESIGN OF.....QUASI-RESONANT CONVERTER

Figure 6-12b ARM-7 control board

## 6.6 Coreless IGBT Gate Driver

The design of IGBT driver circuit is very important for the satisfactory performance of IGBT.

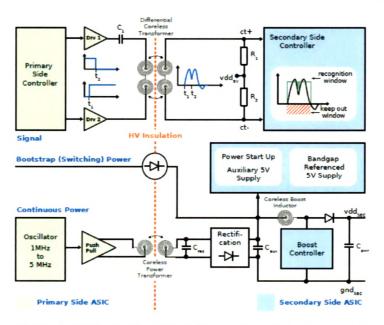

The gate drive circuit as shown in Figure 6-13 is built around a primary and a secondary ASIC (application specific integrated circuit). The ASICs contain all integrated circuitry necessary for implementing the two main functions of a gate driver: First, to transmit signals between primary and secondary side, and second, to provide insulation and power supply for the secondary side.

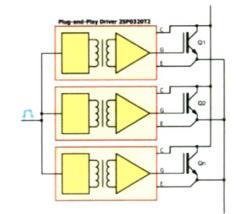

Figure 6-13 Block diagram of the coreless gate drive system

There are chip external coreless transformers on the PCB between primary and secondary side. These coreless transformers consist of spiral windings that are stacked on top of each other and that are separated by the PCB insulation material. No magnetic flux guidance, such as a ferrite core, is used.

## 6.7 New Generation Scale-2 IGBT-Driver Circuits

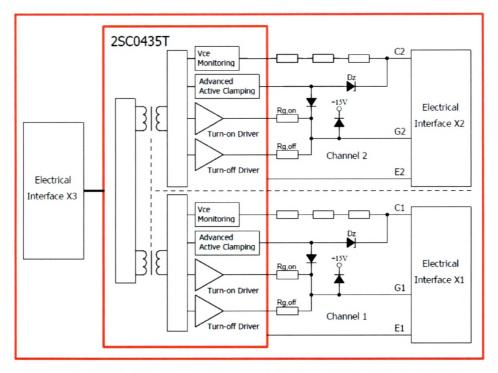

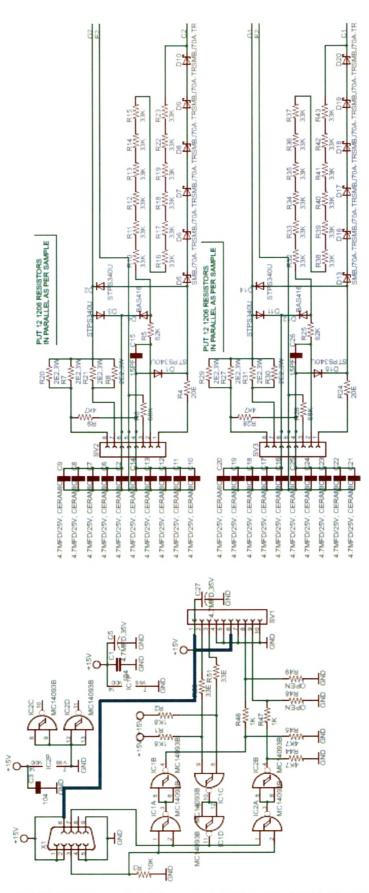

Figure 6-14 Basic Schematic of the gate drive board with 2SC0435T driver

The Scale-2 driver board contains all necessary components for optimal and safe driving of IGBT modules: gate clamping, active-clamping diodes (overvoltage protection at turn-off), Vce monitoring (short-circuit protection) as well as the input electrical connector and both output electrical connectors to connect both the power switch. It is equipped with usual protection functions such as Vce monitoring for short-circuit protection, operation inhibit after fault, supply under voltage shutdown and status feedback. It also features advanced active-clamping function and very low propagation delay time.

The 2SC0435T is the most compact driver core in its power range with a footprint of only 57.2 x 51.6mm and an insertion height of max. 20mm. It combines a complete two-channel driver core with all components required for driving, such as an isolated DC/DC converter, short-circuit protection, advanced active clamping as well as supply voltage monitoring. Each of the two output channels is electrically isolated from the primary side and the other secondary channel.

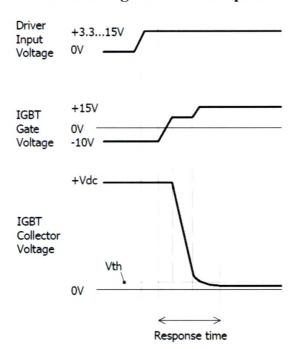

An output current of 35A and 4W drive power is available per channel, making the 2SC0435T an ideal driver platform for universal usage in medium and high-power applications. The driver provides

a gate voltage swing of +15V/-10V. The turn-on voltage is regulated to maintain a stable 15V regardless of the output power level.

Its outstanding EMC allows safe and reliable operation in even hard industrial applications.

## Vce monitoring/short-circuit protection

The basic Vce monitoring circuit of Scale-2 board is illustrated in Figure 6-14. Both IGBT collectoremitter voltages are measured with a resistor network. Vce is checked after the response time (as shown in Figure 6-15) at turn-on to detect a short circuit. If this voltage is higher than the programmed threshold Vth, the drier detects a short circuit at the IGBT and signals it immediately to the corresponding SOx output. The corresponding IGBT is immediately switched off. The IGBT is kept off and the fault is shown at pin SOx as long as the blocking time is active.

Figure 6-15 Turn-on characteristic of an IGBT

The blocking time is applied independently to each channel. It starts when Vce exceeds the threshold of the Vce monitoring circuit. This de-saturation function is for short circuit detection only and cannot provide over current protection. Hence over current protection is directly provided through micro-controller as seen in Figure 6-7.

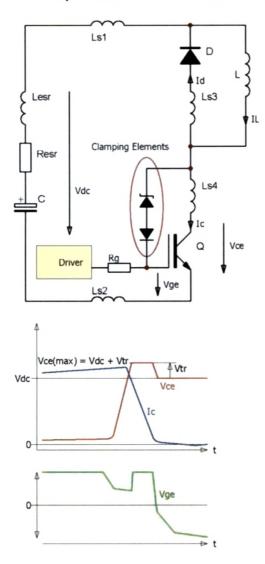

## Active clamping

Parasitic inductances in IGBT modules and converter circuits cannot be completely eliminated for

physical reasons, and their influence on the system behavior cannot be neglected. The current change caused by turning off the IGBT produces voltage transients at its collector, as shown in the upper part of Figure 6-16.

The commutation speed and thus, the turn-off over-voltage at an IGBT can, in principle, be affected by the turn-off gate resistance Rg(off). This technique is used particularly at lower powers.

Figure 6-16 Typical characteristic at IGBT turn-off

However, Rg(off) must then be dimensioned for overload conditions such as turn-off of the double rated current, short circuit and a temporarily increased link circuit voltage. In normal operation this results in increased switching losses and turn-off delays, which reduces the usability of the modules. So this simple method is unsuitable for modern high-power modules.

Simple Active Clamping has already been used for some time to protect IGBTs. Active clamping means the direct feedback of the collector potential to the gate via an element with an avalanche characteristic. Figure 6-17 (upper part) shows the principle on the basis of an IGBT switch.

The feedback branch consists of a clamping element, as a rule comprising a series of transient voltage suppressors (TVS). If the collector-emitter voltage exceeds the approximate breakdown voltage of the clamping element, a current flows via the feedback to the gate of the IGBT and raises its potential, so that the rate of change of the collector current is reduced and a stable condition results. The voltage across the IGBT is then determined by the design of the clamping element. The IGBT operates in the active range of its output characteristic and converts the energy stored in the stray inductance into heat. The continues until the clamping process stray inductances have been demagnetized. The fundamental relationships involved here on the basis of typical curves are illustrated in the lower part of Figure 6-17.

Figure 6-17 Principle of an IGBT driver with Active Clamping

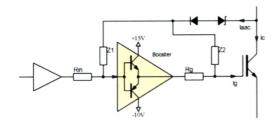

## Advanced active clamping

Simple Active Clamping is traditionally used only to protect the semiconductor in the event of overload. Consequently, the clamping elements are never subjected to recurrent pulse operation.

The problem of repetitive operation takes the following form: modern high power IGBTs are optimally driven with gate resistors in the range from 0.1 to several ohms. For turn-off, the driver supplies an output voltage of -10V. However, the Active Clamping Circuit must raise the gate voltage temporarily to about +15V, in order to reduce the rate of current change. This produces a voltage drop of 25V across the gate resistor. A high current is absorbed by the driver, which flows through the

#### DEVELOPMENT AND DESIGN OF.....QUASI-RESONANT CONVERTER

Active Clamping circuit, where it produces high losses and additional voltage drops. The simple Active Clamping circuit is consequently unsuitable for repetitive operation.

An improved Active Clamping circuit has been presented in Figure 6-18. Here, the base of the chain of clamping diodes is, as usual, connected to the gate of the IGBT, but additionally to the input of a booster stage. The driver voltage is consequently raised as soon as a current flows through the

clamping element. The driver stage now no longer draws any current from the clamping element, and the current flowing through the latter is then available exclusively for charging the gate. The voltage drop and power loss in the clamping diodes can thus be dramatically reduced.

Figure 6-18 Principle of an IGBT driver with Advanced Active Clamping

The final board shown in Figure 6-22 supports the advanced active clamping based on this principle: when active clamping is activated, the turn-off MOSFET of the driver is switched off in order to improve the effectiveness of the active clamping and to reduce the losses in the TVS.

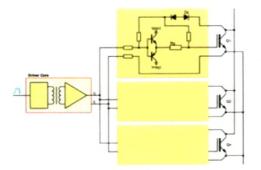

## **Intelligent paralleling**

Parallel-connected IGBTs are conventionally driven by a common driver, with individual gate and

emitter resistors for each IGBT. However, modules of the Prime PACK power class require more extensive circuitry: they cannot, for instance, dispense with active clamping [25], which results in solutions such as that proposed in Figure 6-19.

#### Figure 6-19 Principle of a central driver

An alternative approach to driving parallel-connected IGBT modules is to use an individual driver for each module, as shown in Figure 6-20. However, this attractively simple approach was hardly practical in the past because the drivers previously available on the market had excessive runtime differences and jitter, which would have led to an

Figure 6-20 Principle of driving parallel connected IGBTs with individual drivers

### DEVELOPMENT AND DESIGN OF.....QUASI-RESONANT CONVERTER

asymmetrical distribution of the collector currents and losses in the parallel-connected modules. Moreover, previous drivers also failed to offer any scenario for the behavior of parallel-connected drivers in the event of a fault.

A solution is now available with the SCALE-2 driver chipset from CONCEPT [26] [27]. With a runtime of just below 80ns, as shown in Figure 6-21, it is about five times as fast as the preceding generation and 8 to 20 times faster than typical competitor solutions. In addition, the small deviations in the runtimes of the various drivers of  $\leq \pm 4$ ns and the extremely low jitter of  $\leq \pm 2$ ns make it ideal for use in the parallel circuit. The low tolerance of these parameters ensures that the parallel-driven IGBTs switch almost simultaneously. As every IGBT module has its own driver, the power of a single driver does not need to be distributed over several IGBTs. So this concept also allows high clock frequencies with parallel circuits.

| Power supply                                      | Remarks                             | Min  | Тур  | Max  | Unit |

|---------------------------------------------------|-------------------------------------|------|------|------|------|

| Supply current Ioc                                | Without load                        |      | 32   |      | mA   |

| Supply current I <sub>OC</sub>                    | F = OHz                             |      | 26   |      | mA   |

| Supply current Icc                                | F = 100 kHz                         |      | 38   |      | mΑ   |

| Coupling capacitance C <sub>k</sub>               | Primary to output, total            |      | 20   |      | рF   |

| Power Supply Monitoring                           | Remarks                             | Min  | Тур  | Max  | Unit |

| Supply threshold V <sub>ot</sub>                  | Primary side, clear fault           | 11.9 | 12.6 | 13.3 | v    |

|                                                   | Primary side, set fault (Note 12)   | 11.3 | 12.0 | 12,7 | ٧    |

| Monitoring hysteresis                             | Primary side, set/clear fault       | 0.35 |      |      | ۷    |

| Supply threshold $V_{\rm ISOx}\text{-}V_{\rm Fx}$ | Secondary side, clear fault         | 12.1 | 12.6 | 13.1 | ۷    |

|                                                   | Secondary side, set fault (Note 13) | 11.5 | 12.0 | 12.5 | ٧    |

| Monitoring hysteresis                             | Secondary side, set/clear fault     | 0.35 |      |      | ٧    |

| Supply threshold Vex-VCOHx                        | Secondary side, clear fault         | 5    | 5.15 | 5,3  | ۷    |

|                                                   | Secondary side, set fault (Note 13) | 4,7  | 4,85 | 5    | ٧    |

| Monitoring hysteresis                             | Secondary side, set/clear fault     | 0.15 |      |      | ٧.   |

| Logic Inputs and Outputs                          | Remarks                             | Min  | Тур  | Max  | Unit |

| Input bias current                                | V(INx) > 3V                         |      | 190  |      | μА   |

| Turn-on threshold                                 | V(INx)                              |      | 2.6  |      | v    |

| Turn-off threshold                                | V(INx)                              |      | 1.3  |      | ۷    |

| SOx output voltage                                | Failure condition, I(SOx)<20mA      |      |      | 0.7  | ٧    |

| Short-Circuit Protection                          | Remarks                             | Min  | Тур  | Max  | Unit |

| Current through pin REFx                          | R(REFx, VEx)<70kΩ                   |      | 150  |      | μА   |

| Minimum response time                             | Note 9                              |      | 1.2  |      | μs   |

| Minimum blocking time                             | Note 10                             |      | 9    |      | μs   |

| Timing Characteristics                            | Remarks                             | Min  | Тур  | Max  | Unit |

| Tum-on delay t <sub>e(m)</sub>                    | Note 6                              |      | 85   |      | ns   |

| Turn-off delay toton                              | Note 6                              |      | 70   |      | กร   |

| Jitter of turn-on delay                           | Note 17                             |      | ±3   |      | ns   |

| Jitter of turn-off delay                          | Note 17                             |      | ±3   |      | ns   |

| Output rise time trout                            | Note 7                              |      | 20   |      | กร   |

| Output fail time t <sub>Kout</sub>                | Note 7                              |      | 20   |      | ns   |

| Transmission delay of fault state                 | Note 14                             |      | 400  |      | ns   |

Figure 6-21 Electrical characteristics of 2SC0435T

Figure 6-22 Final Schematic of the gate drive board with 2SC0435T driver

.

# 6.8 Summary

In this chapter the Micro-controller Board & Embedded controller board based on Arm-7 are developed and tested.

The different driving methods for IGBT are discussed & SCALE-2 driver is used to build the driver board.

The main finding of this discussion revels following:

.

.

In comparison with other driving methods, active clamping allows enhanced utilization of the IGBT modules during normal operation by increasing the switching speed and therefore reducing switching losses. The overvoltage at fault-current turn-off is also managed by active clamping.